# FLIP-FLOPS

Gates are decision-making elements. As shown in the preceding chapter, they can perform binary addition and subtraction. But decision-making elements are not enough. A computer also needs *memory elements*, devices that can store a binary digit. This chapter is about memory elements called *flip-flops*.

## 7-1 RS LATCHES

A flip-flop is a device with two stable states; it remains in one of these states until triggered into the other. The *RS* latch, discussed in this section, is one of the simplest flip-flops.

## **Transistor Latch**

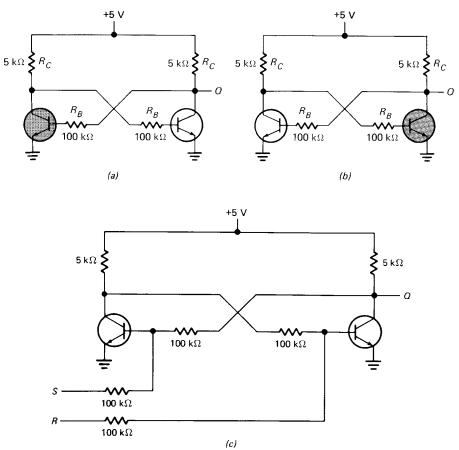

In Fig. 7-1a each collector drives the opposite base through a 100-k $\Omega$  resisitor. In a circuit like this, one of the transistors is saturated and the other is cut off.

For instance, if the right transistor is saturated, its collector voltage is approximately 0 V. This means that there is no base drive for the left transistor, so it cuts off and its collector voltage approaches +5 V. This high voltage produces enough base current in the right transistor to sustain its saturation. The overall circuit is *latched* with the left transistor cut off (dark shading) and the right transistor saturated. Q is approximately 0 V.

By a similar argument, if the left transistor is saturated, the right transistor is cut off. Figure 7-1b illustrates this other state. Q is approximately 5 V for this condition.

Output Q can be low or high, binary 0 or 1. If latched as shown in Fig. 7-1a, the circuit is storing a binary 0 because

$$Q = 0$$

On the other hand, when latched as shown in Fig. 7-1b, the circuit stores a binary 1 because

$$O = 1$$

## **Control Inputs**

To control the bit stored in the latch, we can add the inputs shown in Fig. 7-1c. These control inputs will be either low (0 V) or high (+5 V). A high *set* input S forces the left transistor to saturate. As soon as the left transistor saturates, the overall circuit latches and

$$Q = 1$$

Once set, the output will remain a 1 even though the S input goes back to 0 V.

A high *reset* input *R* drives the right transistor into saturation. Once this happens, the circuit latches and

$$Q = 0$$

The output stays latched in the 0 state, even though the R input returns to a low.

In Fig. 7-1c, Q represents the stored bit. A complementary output  $\overline{Q}$  is available from the collector of the left transistor. This may or may not be used, depending on the application.

#### **Truth Table**

Table 7-1 summarizes the operation of the transistor latch. With both control inputs low, no change can occur in the output and the circuit remains latched in its last state. This condition is called the *inactive state* because nothing changes.

TABLE 7-1. TRANSISTOR LATCH

| R | S | Q  | Comments  |

|---|---|----|-----------|

| 0 | 0 | NC | No change |

| 0 | 1 | 1  | Set       |

| 1 | 0 | 0  | Reset     |

| 1 | 1 | *  | Race      |

Fig. 7-1 (a) Latched state; (b) alternative state; (c) trigger inputs.

When R is low and S is high, the circuit sets the Q output to a high. On the other hand, if R is high and S is low, the Q output resets to a low.

## **Race Condition**

Look at the last entry in Table 7-1. R and S are high simultaneously. This is called a *race condition*; it is never used because it leads to unpredictable operation.

Here's why. If both control inputs are high, both transistors saturate. When the R and S inputs return to low, both transistors try to come out of saturation. It is a race between the transistors to see which one desaturates first. The faster transistor (the one with the shorter saturation delay time) will win the race and latch the circuit. If the faster transistor is on the left side of Fig. 7-1c, the Q output will be low. If the faster transistor is on the right side, the Q output will go high. In mass production, either transistor can be faster; therefore, the Q output is unpredictable. This is why the race condition must be avoided.

Here's how to recognize a race condition. If simultaneously changing both inputs to a memory element leads to an unpredictable output, you've got a race condition. With the transistor latch, R=1 and S=1 is a race condition

because simultaneously returning R and S to 0 forces Q into a random state.

From now on, an asterisk in a truth table (see Table 7-1) indicates a race condition, sometimes called a forbidden or invalid state.

## **NOR Latches**

A discrete circuit like Fig. 7-1c is rarely used because we are in the age of integrated circuits. Nowadays, you build RS latches with NOR gates or NAND gates.

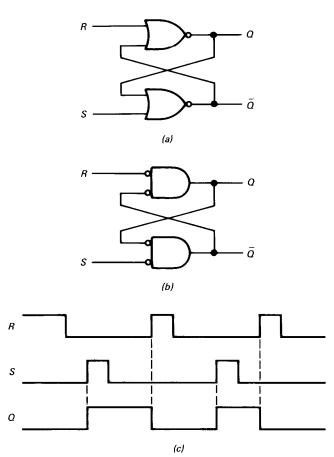

Figure 7-2a shows how it's done with NOR gates. Figure 7-2b is the De Morgan equivalent. As shown in Table 7-2, a low R and a low S give us the inactive state; the circuit stores or remembers. A low R and a high S represent the set state, while a high R and a low S give the reset state. Finally, a high R and a high S produce a race condition; therefore, we must avoid R = 1 and S = 1 when using a NOR latch.

Figure 7-2c is a *timing diagram;* it shows how the input signals interact to produce the output signal. As you see, the Q output goes high when S goes high. Q remains high after S goes low. Q returns to low when R goes high, and stays low after R returns to low.

TABLE 7-2. NOR LATCH

| R | S | Q  | Comment   |

|---|---|----|-----------|

| 0 | 0 | NC | No change |

| 0 | 1 | 1  | Set       |

| 1 | 0 | 0  | Reset     |

| 1 | 1 | *  | Race      |

|   |   |    |           |

Fig. 7-2 (a) NOR latch; (b) De Morgan equivalent; (c) timing diagram.

#### **NAND Latches**

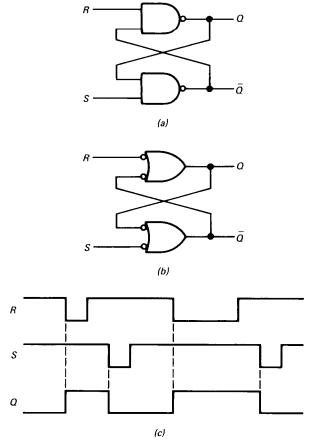

If you prefer using NAND gates, you can build an RS latch as shown in Fig. 7-3a. Sometimes it is convenient to draw the De Morgan equivalent shown in Fig. 7-3b. In either case, a low R and a high S set Q to high; a high R and a low S reset Q to low.

Because of the NAND-gate inversion, the inactive and race conditions are reversed. In other words, R=1 and S=1 becomes the inactive state; R=0 and S=0 becomes the race condition (see Table 7-3). Therefore, whenever you use a NAND latch, you must avoid having both inputs low at the same time. (To remember the race condition for a NAND latch, glance at Fig. 7-3b. If R=0 and S=0, then Q=1 and  $\overline{Q}=1$ ; both outputs are the same, indicating an invalid condition.)

TABLE 7-3, NAND LATCH

| R | S | Q  | Comment   |

|---|---|----|-----------|

| 0 | 0 | *  | Race      |

| 0 | 1 | 1  | Set       |

| 1 | 0 | 0  | Reset     |

| 1 | 1 | NC | No change |

Fig. 7-3 (a) NAND latch; (b) De Morgan equivalent; (c) timing diagram.

Figure 7-3c shows the timing diagram for a NAND latch. R and S are normally high to avoid the race condition. Only one of them goes low at any time. As you see, the Q output goes high whenever R goes low; the Q output goes low whenever S goes low.

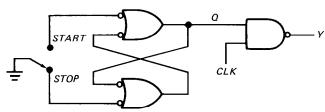

## **Switch Debouncers**

RS latches are often used as switch debouncers. Whenever you throw a switch from the open to the closed position, the contacts bounce and the switch alternately makes and breaks for a few milliseconds before finally settling in the closed position. One way to eliminate the effects of contact bounce is to use an RS latch in conjunction with the switch. The following example explains the idea.

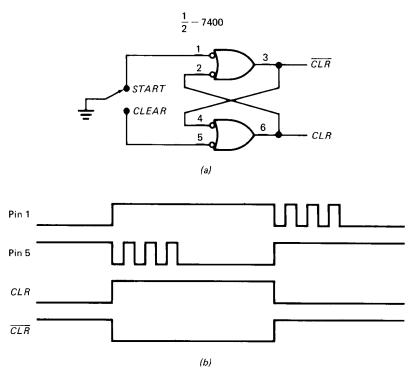

Fig. 7-4 Switch debouncer.

#### EXAMPLE 7-1

Figure 7-4a shows a switch debouncer. What does it do?

#### SOLUTION

As discussed in Chap. 4, floating TTL inputs are equivalent to high inputs. With the switch in the START position, pin 1 is low and pin 5 is high; therefore,  $\overline{CLR}$  is high and CLR is low. When the switch is thrown to the CLEAR position, pin 1 goes high, as shown in Fig. 7-4b. Because of contact bounce, pin 5 goes alternately low and high for a few milliseconds before settling in the low state, symbolized by the ideal pulses of Fig. 7-4b. The first time pin 5 goes low, the latch sets, CLR going high and  $\overline{CLR}$  going low. Subsequent bounces have no effect on CLR and  $\overline{CLR}$  because the latch stays set.

Similarly, when the switch is thrown back to START, pin 1 bounces low and high for a while. The first time pin 1 goes low, CLR goes back to low and  $\overline{CLR}$  to high. Later bounces have no effect on CLR and  $\overline{CLR}$ .

Registers need clean signals like CLR and  $\overline{CLR}$  of Fig. 7-4b to operate properly. If the bouncing signals on pins 1 and 5 drove the registers, the operation would be erratic. This is why you often see RS latches used as switch debouncers.

#### 7-2 LEVEL CLOCKING

Computers use thousands of flip-flops. To coordinate the overall action, a square-wave signal called the *clock* is sent to each flip-flop. This signal prevents the flip-flops from changing states until the right time.

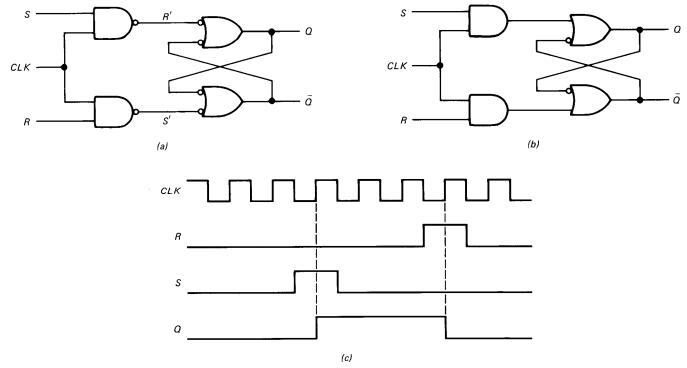

#### **Clocked Latch**

In Fig. 7-5a a pair of NAND gates drive a NAND latch. S and R signals drive the input gates. To avoid confusion, the inner control signals are labeled R' and S'. The NAND latch works as previously described; a low R' and a high S' set Q to 1, whereas a high R' and a low S' reset Q to 0. Furthermore, a low R' and S' represent the race condition; therefore, R' and S' are normally high when the latch is inactive. Because of the inversion through the input NAND gates, the S input has to drive the upper NAND input and the R input must drive the lower NAND input.

## **Double Inversions Cancel**

When analyzing the operation of this and similar circuits, remember that a double inversion (two bubbles in a series path) cancels out; this makes it appear as though two AND gates drove OR gates, as shown in Fig. 7-5b. In this way, you can see at a glance that a high S and high CLK force

Fig. 7-5 (a) Clocked latch; (b) equivalent circuit; (c) timing diagram.

Q to go high. In other words, even though you are looking at Fig. 7-5a, in your mind you should see Fig. 7-5b.

## **Positive Clocking**

In Fig. 7-5a the clock is a square-wave signal. Because the clock (abbreviated CLK) drives both NAND gates, a low CLK prevents S and R from controlling the latch. If a high S and a low R drive the gate inputs, the latch must wait until the clock goes high before Q can be set to 1. Similarly, given a low S and a high R, the latch must wait for a high CLK before Q can reset to 0. This is an example of positive clocking, making a latch wait until the clock signal is high before the output can change.

Negative clocking is similar. Visualize an inverter between CLK and the input gates of Fig. 7-5a. In this case, the latch must wait until CLK is low before the output can change.

Positive and negative clocking are often called *level* clocking because the flip-flop responds to the level (high or low) of the clock signal. Level clocking is the simplest way to control flip-flops with a clock. Later, we will discuss more advanced methods called edge triggering and master-slave clocking.

#### **Race Condition**

What about the race condition? When the clock is low in Fig. 7-5a, R' and S' are high, which is a stable condition. The only way to get a race condition is to have a high

CLK, high R, and high S. Therefore, normal operation of this circuit requires that R and S never both be high when the clock goes high.

#### **Timing Diagram and Truth Table**

Figure 7-5c shows the timing diagram. Q goes high when S is high and CLK goes high. Q returns to the low state when R is high and CLK goes high. Using a common CLK signal to drive many flip-flops allows us to synchronize the operation of the different sections of a computer.

Table 7-4 summarizes the operation of the clocked NAND latch. When the clock is low, the output is latched in its last state. When the clock goes high, the circuit will set if S is high or reset if R is high. CLK, R, and S all high is a race condition, which is never used deliberately.

TABLE 7-4. CLOCKED NAND LATCH

| CLK | R | S | Q  |

|-----|---|---|----|

| 0   | 0 | 0 | NC |

| 0   | 0 | 1 | NC |

| 0   | 1 | 0 | NC |

| 0   | 1 | 1 | NC |

| 1   | 0 | 0 | NC |

| 1   | 0 | 1 | 1  |

| 1   | 1 | 0 | 0  |

| 1   | 1 | 1 | *  |

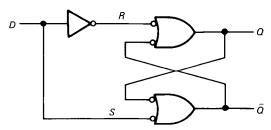

## 7-3 D LATCHES

Since the RS flip-flop is susceptible to a race condition, we will modify the design to eliminate the possibility of a race condition. The result is a new kind of flip-flop known as a D latch.

**Fig. 7-6** *D* latch.

#### Unclocked

Figure 7-6 shows one way to build a D latch. Because of the inverter, data bit D drives the S input of a NAND latch and the complement  $\overline{D}$  drives the R input. Therefore, a high D sets the latch, and a low D resets it. Table 7-5 summarizes the operation of the D latch. Especially important, there is no race condition in this truth table. The inverter guarantees that S and R will always be in opposite states; therefore, it's impossible to set up a race condition in the D latch.

The *D* latch of Fig. 7-6 is unclocked; it will set or reset as soon as *D* goes high or low. An unclocked flip-flop like this is almost never used.

TABLE 7-5. UNCLOCKED D LATCH

| Q |

|---|

| 0 |

| 1 |

|   |

TABLE 7-6. CLOCKED D LATCH

| CLK | D | Q  |

|-----|---|----|

| 0   | X | NC |

| 1   | 0 | 0  |

| 1   | 1 | 1  |

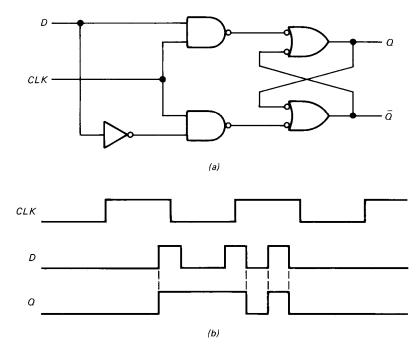

#### Clocked

Figure 7-7a is level-clocked. A low CLK disables the input gates and prevents the latch from changing states. In other words, while CLK is low, the latch is in the inactive state and the circuit stores or remembers. When CLK is high, D controls the output. A high D sets the latch, while a low D resets it.

Table 7-6 summarizes the operation. X represents a don't-care condition; it stands for either 0 or 1. While *CLK* is low, the output cannot change, no matter what *D* is. When *CLK* is high, however, the output equals the input

$$Q = D$$

Figure 7-7b shows a timing diagram. If the clock is low, the circuit is latched and the Q output cannot be changed. While the clock is high, however, Q equals D; when D goes high, Q goes high; when D goes low, Q goes low. The latch is transparent, meaning that the output follows the value of D while the clock is high.

Fig. 7-7 Clocked D latch.

## Disadvantage

Because the D latch is level-clocked, it has a serious disadvantage. While the clock is high, the output follows the value of D. Transparent latches may be all right in some applications but not in the computer circuits we will be discussing. To be truly useful, the circuit of Fig. 7-7a needs a slight modification.

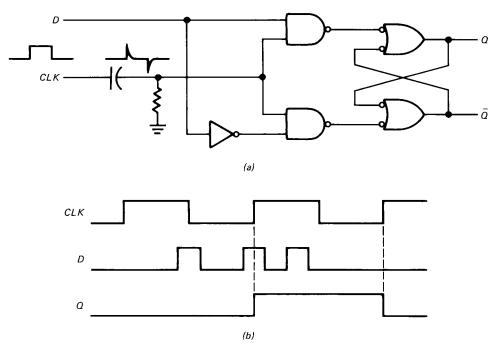

# 7-4 EDGE-TRIGGERED D FLIP-FLOPS

Now we're ready to talk about the most common type of D flip-flop. What a practical computer needs is a D flip-flop that samples the data bit at a unique instant.

## **Edge Triggering**

Figure 7-8a shows an RC circuit at the input of a D flipflop. By deliberate design, the RC time constant is much smaller than the clock's pulse width. Because of this, the capacitor can charge fully when CLK goes high; this exponential charging produces a narrow positive voltage spike across the resistor. Later, the trailing edge of the clock pulse results in a narrow negative spike.

The narrow positive spike enables the input gates for an instant; the narrow negative spike does nothing. The effect is to activate the input gates during the positive spike, equivalent to sampling the value of D for an instant. At this unique time, D and its complement hit the flip-flop inputs, forcing Q to set or reset.

TABLE 7-7. EDGE-TRIGGERED D FLIP-FLOP

| CLK          | D | Q  |

|--------------|---|----|

| 0            | X | NC |

| 1            | X | NC |

| $\downarrow$ | X | NC |

| <b>↑</b>     | 0 | 0  |

| 1            | 1 | 1  |

This kind of operation is called *edge triggering* because the flip-flop responds only when the clock is changing states. The triggering in Fig. 7-8a occurs on the positive-going edge of the clock; this is why it's referred to as *positive-edge triggering*.

Figure 7-8b illustrates the action. The crucial idea is that the output changes only on the rising edge of the clock. In other words, data is stored only on the positive-going edge.

Table 7-7 summarizes the operation of the positive-edgetriggered D flip-flop. The up and down arrows represent the rising and falling edges of the clock. The first three entries indicate that there's no output change when the clock is low, high, or on its negative edge. The last two entries indicate an output change on the positive edge of the clock. In other words, input data D is stored only on the positive-going edge of the clock.

Fig. 7-8 Edge-triggered D flip-flop.

## **Edge Triggering versus Level Clocking**

When a circuit is edge-triggered, the output can change only on the rising (or falling) edge of the clock. But when the circuit is level-clocked, the output can change while the clock is high (or low). With edge triggering, the output can change only at one instant during the clock cycle; with level clocking, the output can change during an entire half cycle of the clock.

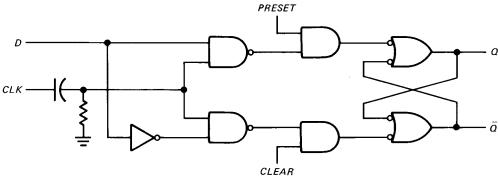

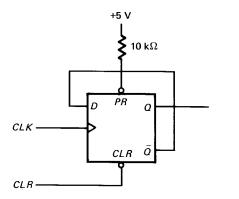

### Preset and Clear

When power is first applied, flip-flops come up in random states. To get some computers started, an operator has to push a master reset button. This sends a *clear* (reset) signal to all flip-flops. Also, it is necessary in some computers to *preset* (synonymous with "set") certain flip-flops before a computer run.

Figure 7-9 shows how to include both functions in a *D* flip-flop. The edge triggering is the same as previously described. In addition, the AND gates allow us to slip in a low *PRESET* or low *CLEAR* when desired. A low *PRESET* forces *Q* to equal 1; a low *CLEAR* resets *Q* to 0.

Table 7-8 summarizes the circuit action. When *PRESET* and *CLEAR* are both low, we get a race condition; therefore, *PRESET* and *CLEAR* should be kept high when inactive. Take *PRESET* low by itself and you set the flip-flop; take *CLEAR* low by itself and you reset the flip-flop. As shown in the remaining entries, the output changes only on the positive-going edge of the clock.

Preset is sometimes called *direct set*, and clear is sometimes called *direct reset*. The word "direct" means unclocked. For instance, the clear signal may come from a push button; regardless of what the clock is doing, the output will reset when the operator pushes the clear button.

The preset and clear inputs override the other inputs; they have first priority. For example, when *PRESET* goes low, the *Q* output goes high and stays there no matter what the *D* and *CLK* inputs are doing. The output will remain high as long as *PRESET* is low. Therefore, the normal procedure in presetting is to take the *PRESET* low tempo-

TABLE 7-8. D FLIP-FLOP WITH PRESET AND CLEAR

| PRESET | CLEAR | CLK          | D | Q    |

|--------|-------|--------------|---|------|

| 0      | 0     | X            | X | *    |

| 0      | 1     | X            | X | 1    |

| 1      | 0     | X            | X | 0    |

| 1      | 1     | 0            | X | l NC |

| 1      | 1     | 1            | X | l NC |

| 1      | 1     | $\downarrow$ | X | NC   |

| 1      | 1     | 1            | 0 | 0    |

| 1      | 1     | 1            | 1 | 1    |

rarily, then return it to high. Similarly, for the clear function: take *CLEAR* low briefly to reset the flip-flop, then take it back to high to allow the circuit to operate.

## Direct-Coupled Edge-Triggered D Flip-Flop

Integrated D flip-flops do not use RC circuits to get narrow spikes because capacitors are difficult to fabricate on a chip. Instead, a variety of direct-coupled designs is used. As an example, Fig. 7-10 shows a positive-edge-triggered D flip-flop. This direct-coupled circuit has no capacitors, only NAND gates. The analysis is too long and complicated to go into here, but the idea is the same as previously discussed. The circuit responds only during the brief instant the clock switches from low to high. That is, data bit D is stored only on the positive-going edge of the clock.

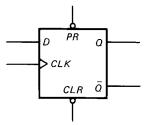

## Logic Symbol

Figure 7-11 is the symbol of a positive-edge-triggered D flip-flop. The CLK input has a small triangle, a reminder of the edge triggering. When you see this schematic symbol, remember what it means: the D input is stored on the rising edge of the clock.

Fig. 7-9 Edge-triggered D flip-flop with preset and clear.

Fig. 7-10 Direct-coupled edge-triggered D flip-flop.

Fig. 7-11 Logic symbol for edge-triggered D flip-flop.

Figure 7-11 also includes preset (*PR*) and clear (*CLR*) inputs. The bubbles indicate an *active low state*. In other words, the preset and clear inputs are high when inactive. To preset the flip-flop, the preset input must go low temporarily and then be returned to high. Similarly, to reset the flip-flop, the clear input must go low, then back to high.

The same idea applies to circuits discussed later. A bubble at an input means an active low state: the input has to go low to produce an effect. When no bubble is present, the input has to go high to have an effect.

#### **Propagation Delay Time**

Diodes and transistors cannot switch states instantaneously. It always takes a small amount of time to turn a diode on or off. Likewise, it takes a time for a transistor to switch from saturation to cutoff or vice versa. For bipolar diodes and transistors, switching time is in the nanosecond region.

Switching time is the main cause of *propagation delay* time  $t_p$ . This represents the amount of time it takes for the output of a gate or flip-flop to change states. For instance,

if the data sheet of a D flip-flop indicates a  $t_p$  of 10 ns, it takes approximately 10 ns for Q to change states after D has been sampled by the clock edge.

Propagation delay time is so small that it's negligible in many applications, but in high-speed circuits you have to take it into account. If a flip-flop has a  $t_p$  of 10 ns, this means that you have to wait 10 ns before the output can trigger another circuit.

## **Setup Time**

Stray capacitance at the D input (plus other factors) makes it necessary for data bit D to be at the input before the CLK edge arrives. The *setup time t*<sub>setup</sub> is the minimum length of time the data bit must be present before the CLK edge hits

For instance, if the data sheet of a D flip-flop indicates a  $t_{\text{setup}}$  of 15 ns, the data bit to be stored must be at the D input at least 15 ns before the CLK edge arrives; otherwise, the IC manufacturer does not guarantee correct sampling and storing.

#### **Hold Time**

Furthermore, data bit D has to be held long enough for the internal transistors to switch states. Only after the transition is assured can we allow data bit D to change. Hold time  $t_{hold}$  is the minimum length of time the data bit must be present after the CLK edge has struck.

For example, if  $t_{\text{setup}}$  is 15 ns and  $t_{\text{hold}}$  is 5 ns, the data bit has to be at the D input at least 15 ns before the CLK edge arrives and held at least 5 ns after the CLK edge hits.

# 7-5 EDGE-TRIGGERED JK FLIP-FLOPS

The next chapter shows you how to build a counter, the electronic equivalent of a binary odometer. When it comes to circuits that count, the *JK flip-flop* is the ideal memory element to use.

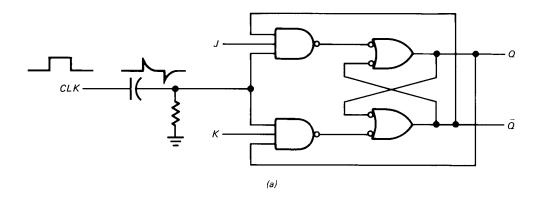

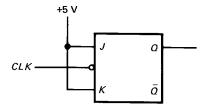

#### Circuit

Figure 7-12a shows one way to build a *JK* flip-flop. As before, an *RC* circuit with a short time constant converts the rectangular *CLK* pulse to narrow spikes. Because of the double inversion through the NAND gates, the circuit is positive-edge-triggered. In other words, the input gates are enabled only on the rising edge of the clock.

#### **Inactive**

The J and K inputs are control inputs; they determine what the circuit will do on the positive clock edge. When J and K are low, both input gates are disabled and the circuit is inactive at all times including the rising edge of the clock.

#### Reset

When J is low and K is high, the upper gate is disabled; so there's no way to set the flip-flop. The only possibility is reset. When Q is high, the lower gate passes a reset trigger as soon as the positive clock edge arrives. This forces Q to become low. Therefore, J=0 and K=1 means that a rising clock edge resets the flip-flop.

#### Set

When J is high and K is low, the lower gate is disabled; so it's impossible to reset the flip-flop. But you can set the flip-flop as follows. When Q is low,  $\overline{Q}$  is high; therefore, the upper gate passes a set trigger on the positive clock edge. This drives Q into the high state. That is, J=1 and K=0 means that the next positive clock edge sets the flip-flop.

## Toggle

When J and K are both high, it is possible to set or reset the flip-flop, depending on the current state of the output. If Q is high, the lower gate passes a reset trigger on the

Fig. 7-12 (a) Edge-triggered JK flip-flop; (b) timing diagram.

TABLE 7-9. POSITIVE-EDGE-TRIGGERED JK FLIP-FLOP

| CLK          | J | K | Q      |

|--------------|---|---|--------|

| 0            | X | X | NC     |

| 1            | X | X | NC     |

| $\downarrow$ | X | X | NC     |

| X            | 0 | 0 | NC     |

| 1            | 0 | i | 0      |

| <b>↑</b>     | 1 | 0 | 1      |

| <b>↑</b>     | 1 | 1 | Toggle |

next positive clock edge. On the other hand, when Q is low, the upper gate passes a set trigger on the next positive clock edge. Either way, Q changes to the complement of the last state. Therefore, J=1 and K=1 means that the flip-flop will toggle on the next positive clock edge. ("Toggle" means switch to opposite state.)

## **Timing Diagram**

The timing diagram of Fig. 7-12b is a visual summary of the action. When J is high and K is low, the rising clock edge sets Q to high. On the other hand, when J is low and K is high, the rising clock edge resets Q to low. When J and K are high simultaneously, the output toggles on each rising clock edge.

### **Truth Table**

Table 7-9 summarizes the operation. The circuit is inactive when the clock is low, high, or on its negative edge. Likewise, the circuit is inactive when J and K are both low. Output changes occur only on the rising edge of the clock, as indicated by the last three entries of the table. The output either resets, sets, or toggles.

#### Racing

The JK flip-flop shown in Fig. 7-12a has to be edgetriggered to avoid oscillations. Why? Assume that the circuit is level-clocked. In other words, assume that we remove the RC circuit and run the clock straight into the gates. With a high J, high K, and high CLK, the output will toggle. New outputs are then fed back to the input gates. After two propagation times (input and output gates), the output toggles again. And once more, new outputs return to the input gates. In this way, the output can toggle repeatedly as long as the clock is high. That is, we get oscillations during the positive half cycle of the clock. Toggling more than once during a clock cycle is called racing.

Now assume that we put the RC circuit back in and return to edge triggering. Propagation delay time prevents the JK flip-flop from racing. Here's why. In Fig. 7-12a the outputs change after the positive clock edge has struck. By the time the new Q and  $\overline{Q}$  signals return to the input gates, the positive spikes have decayed to zero. This is why we get only one toggle during each clock cycle.

For instance, if the total propagation delay time from input to output is 20 ns, the outputs change approximately 20 ns after the rising edge of the clock. If the spikes are narrower than 20 ns, the returning Q and  $\overline{Q}$  arrive too late to cause false triggering.

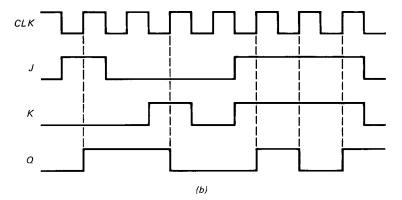

## **Symbols**

As previously mentioned, capacitors are too difficult to fabricate on a chip. This is why manufacturers prefer direct-coupled designs for edge-triggered JK flip-flops. Such designs are too complicated to reproduce here, but you can find them in manufacturers' IC data books.

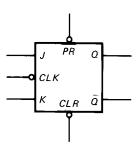

Figure 7-13a is the standard symbol for a positive-edge-triggered JK flip-flop of any design.

Figure 7-13b is the symbol for a JK flip-flop with the preset and clear functions. As usual, PR and CLR have active low states. This means that they are normally high and taken low temporarily to preset or clear the circuit.

Figure 7-13c is another commercially available JK flip-flop. The bubble on the clock input is the standard way to indicate negative-edge triggering. As shown in Table 7-10, the output can change only on the *falling* edge of the clock. The timing diagram of Fig. 7-13d emphasizes this negative-edge triggering.

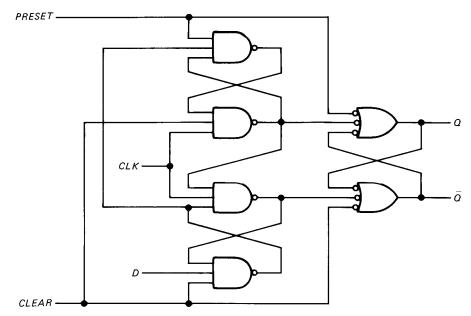

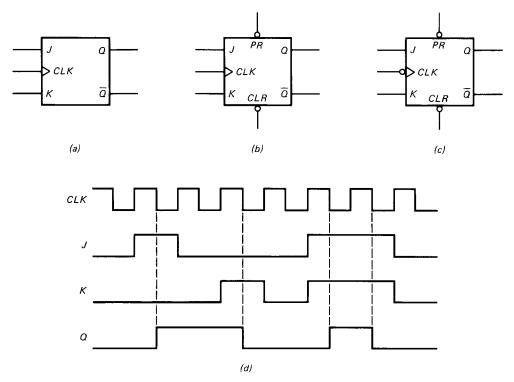

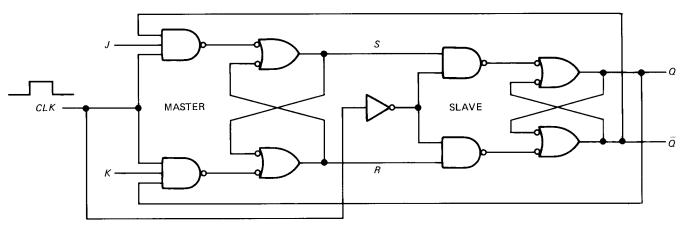

## 7-6 JK MASTER-SLAVE FLIP-FLOP

Figure 7-14 shows a *JK master-slave* flip-flop, another way to avoid racing. A master-slave flip-flop is a combination of two clocked latches; the first is called the *master*, and the second is the *slave*. Notice that the master is positively

TABLE 7-10. NEGATIVE-EDGE-TRIGGERED JK FLIP-FLOP

| CLK          | J | K | Q      |

|--------------|---|---|--------|

| 0            | X | X | NC     |

| 1            | X | X | NC     |

| <b>↑</b>     | X | X | NC     |

| X            | 0 | 0 | NC     |

| $\downarrow$ | 0 | 1 | 0      |

| $\downarrow$ | 1 | 0 | 1      |

| $\downarrow$ | 1 | 1 | Toggle |

**Fig. 7-13** (a) Positive-edge triggering; (b) active low preset and clear; (c) negative-edge triggering; (d) timing diagram.

Fig. 7-14 Master-slave JK flip-flop.

clocked but the slave is negatively clocked. This implies the following:

- 1. While the clock is high, the master is active and the slave is inactive.

- 2. While the clock is low, the master is inactive and the slave is active.

#### Set

To start the analysis, let's assume low Q and high  $\overline{Q}$ . For an input condition of high J, low K, and high CLK, the

master goes into the set state, producing high S and low R. Nothing happens to the Q and  $\overline{Q}$  outputs because the slave is inactive while the clock is high. When the clock goes low, however, the high S and low R force the slave into the set state, producing a high Q and a low  $\overline{Q}$ .

There are two distinct steps in setting the final Q output. First, the master is set while the clock is high. Second, the slave is set while the clock is low. This action is sometimes called cocking and triggering. You cock the master during the positive half cycle of the clock, and you trigger the slave during the negative half cycle of the clock.

#### Reset

When the slave is set, Q is high and  $\overline{Q}$  is low. For the input condition of low J, high K, and high CLK, the master will reset, forcing S to go low and R to go high. Again, no changes can occur in Q and  $\overline{Q}$  because the slave is inactive while the clock is high. When the clock returns to the low state, the low S and high R force the slave to reset; this forces Q to go low and  $\overline{Q}$  to go high.

Again, notice the cocking and triggering. This is the key idea behind the master-slave flip-flop. Every action of the master with a high *CLK* is copied by the slave when the clock goes low.

## Toggle

If the J and K inputs are both high, the master toggles once while the clock is high; the slave then toggles once when the clock goes low. No matter what the master does, the slave copies it. If the master toggles into the set state, the slave toggles into the set state. If the master toggles into the reset state, the slave toggles into the reset state.

## Level Clocking

The master-slave flip-flop is level-clocked in Fig. 7-14. While the clock is high, therefore, any changes in J and K can affect the S and R outputs. For this reason, you normally keep J and K constant during the positive half cycle of the clock. After the clock goes low, the master becomes inactive and you can allow J and K to change.

Fig. 7-15 Symbol for master-slave JK flip-flop.

#### **Symbol**

Figure 7-15 shows the symbol for a JK master-slave flip-flop with preset and clear functions. The bubble on the CLK input reminds us that the output changes when the clock goes low.

#### **Truth Table**

Table 7-11 summarizes the operation of a JK master-slave flip-flop. A low PR and low CLR produces a race condition; therefore, PR and CLR are normally kept at a high voltage

TABLE 7-11. MASTER-SLAVE FLIP-FLOP

| PR | CLR | CLK | J            | K | Q      |

|----|-----|-----|--------------|---|--------|

| 0  | 0   | X   | X            | X | *      |

| 0  | 1   | X   | X            | X | 1      |

| 1  | 0   | X   | $\mathbf{X}$ | X | 0      |

| 1  | 1   | X   | 0            | 0 | NC     |

| 1  | 1   |     | 0            | 1 | 0      |

| 1  | 1   |     | 1            | 0 | 1      |

| 1  | 1   |     | 1            | 1 | Toggle |

when inactive. To clear, you take *CLR* low; to preset, you take *PR* low. In either case, you return them to high when ready to run.

As before, low J and low K produce an inactive state, regardless of the what the clock is doing. If K goes high by itself, the next clock pulse resets the flip-flop. If J goes high by itself, the next clock pulse sets the flip-flop. When J and K are both high, each clock pulse produces one toggle.

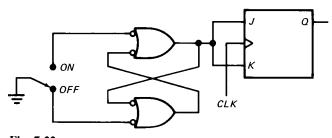

#### EXAMPLE 7-2

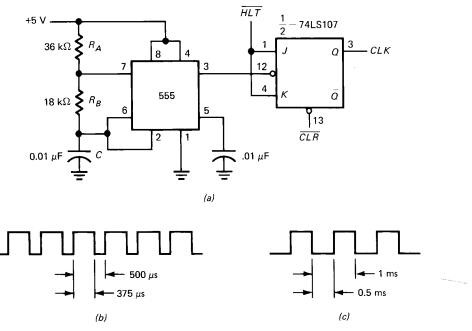

Figure 7-16a shows a *clock generator*. What does it do when  $\overline{HLT}$  is high?

#### SOLUTION

To begin with, the 555 is an IC that can generate a rectangular output when connected as shown in Fig. 7-16a. The frequency of the output is

$$f = \frac{1.44}{(R_A + 2R_B)C}$$

The duty cycle (ratio of high state to period) is

$$D = \frac{R_A + R_B}{R_A + 2R_B}$$

With the values shown in Fig. 7-16a the frequency of the output is

$$f = \frac{1.44}{(36 \,\mathrm{k}\Omega + 36 \,\mathrm{k}\Omega)(0.01 \,\mathrm{\mu F})} = 2 \,\mathrm{kHz}$$

and the duty cycle is

$$D = \frac{36 \,\mathrm{k}\Omega + 18 \,\mathrm{k}\Omega}{36 \,\mathrm{k}\Omega + 36 \,\mathrm{k}\Omega} = 0.75$$

which is equivalent to 75 percent.

Fig. 7-16 Clock generator: (a) circuit; (b) 555 output; (c) JK flip-flop output.

Figure 7-16b illustrates how the output (pin 3) of the 555 looks. Note how the signal is high for 75 percent of the cycle. This unsymmetrical output drives the clock input of a *JK* master-slave flip-flop.

The *JK* master-slave flip-flop toggles once per input cycle; therefore, its output has a frequency of 1 kHz and a duty cycle of 50 percent. One of the reasons for using the flip-flop is to get the symmetrical output shown in Fig. 7-16c.

Another reason for using the flip-flop is to control the starting phase of the clock. A computer run starts with  $\overline{CLR}$  going momentarily low, then back to high. This resets the flip-flop, forcing CLK to go low. Therefore, the starting phase of the CLK signal is always low. You will see the clock generator of Fig. 7-16a again in Chap. 10; remember that the CLK signal has a frequency of 1 kHz, a duty cycle of 50 percent, and starting phase of low.

## **GLOSSARY**

contact bounce The making and breaking of contacts for a few milliseconds after a switch closes.

edge triggering Changing the output state of a flip-flop on the rising or falling edge of a clock pulse.

**flip-flop** A two-state circuit that can remain in either state indefinitely. Also called a bistable multivibrator. An external trigger can change the output state.

**hold time** The minimum amount of time the input signals must be held constant after the clock edge has struck. After a clock edge strikes a flip-flop, the internal transistors need time to change from one state to another. The input control signals (D, or J and K) must be held constant while these internal transistors are switching over.

latch The simplest type of flip-flop, consisting of two cross-coupled NAND or NOR latches.

level clocking A type of triggering in which the output of a flip-flop responds to the level (high or low) of the

clock signal. With positive level clocking, for example, the output can change at any time during the positive half cycle. *master-slave triggering* A type of triggering using two cascaded latches called the master and the slave. The master is cocked during the positive half cycle of the clock, and the slave is triggered during the negative half cycle.

propagation delay time The time it takes for the output of a gate or flip-flop to change after the inputs have changed. race condition An undesirable condition which may exist in a system when two or more inputs change simultaneously. If the final output depends on which input changes first, a race condition exists.

**setup time** The minimum amount of time the inputs to a flip-flop must be present before the clock edge arrives. **toggle** Change of the output to the opposite state in a *JK* flip-flop.

## **SELF-TESTING REVIEW**

Read each of the following and provide the missing words. Answers appear at the beginning of the next question.

- 1. A flip-flop is a \_\_\_\_\_\_\_ element that stores a binary digit as a low or high voltage. With an RS latch a high S and a low R sets the output to \_\_\_\_\_\_; a low S and a high R \_\_\_\_\_\_ the output to low.

- 2. (memory, high, reset) With a NAND latch a low R and a low S produce a \_\_\_\_\_\_ condition. This is why R and S are kept high when inactive. One use for latches is switch debouncers; they eliminate the effects of \_\_\_\_\_ bounce.

- 3. (race, contact) Computers use thousands of flipflops. To coordinate the overall action, a common signal called the \_\_\_\_\_\_\_ is sent to each flip-flop.

With positive clocking the clock signal must be \_\_\_\_\_\_ for the flip-flop to respond. Positive and negative clocking are also called level clocking because the flip-flop responds to the \_\_\_\_\_\_ of the clock, either high or low.

- **4.** (clock, high, level) In a D latch, data bit D drives the S input of a latch, and the complement  $\overline{D}$  drives the R input; therefore, a high D \_\_\_\_\_\_\_ the latch and a low D resets it. Since R and S are always in opposite states in a D latch, the \_\_\_\_\_\_ condition is impossible.

- 5. (sets, race) With a positive-edge-triggered D flipflop, the data bit is sampled and stored on the edge of the clock pulse. Preset and clear

- inputs are often called \_\_\_\_\_\_ set and \_\_\_\_\_ reset. These inputs override the other inputs; they have first priority. When preset goes low, the Q output goes \_\_\_\_\_ and stays there no matter what the D and CLK inputs are doing.

- 6. (rising, direct, direct, high) In a flip-flop, propagation delay time is the amount of time it takes for the \_\_\_\_\_\_ to change after the clock edge has struck. Setup time is the amount of time an input signal must be present \_\_\_\_\_\_ the clock edge strikes. Hold time is the amount of time an input signal must be present \_\_\_\_\_ the clock edge strikes.

- 7. (output, before, after) In a positive-edge-triggered JK flip-flop, a low J and a low K produce the \_\_\_\_\_\_ state. A high J and a high K mean that the output will \_\_\_\_\_ on the rising edge of the clock.

- 8. (inactive, toggle) With a JK master-slave flip-flop the master is cocked when the clock is \_\_\_\_\_\_, and the slave is triggered when the clock is \_\_\_\_\_. This type of flip-flop is usually level-clocked instead of edge-triggered. For this reason, J and K are normally kept \_\_\_\_\_ while the clock is high.

- **9.** (*high*, *low*, *constant*) Since capacitors are too difficult to fabricate on an IC chip, manufacturers rely on various direct-coupled designs for *D* flip-flops and *JK* flip-flops.

## **PROBLEMS**

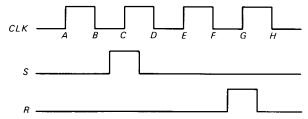

- **7-1.** The waveforms of Fig. 7-17 drive a clocked RS latch (Fig. 7-5a). If Q is low before time A,

- a. At what point does Q become a 1?

- b. When does Q reset to 0?

Fig. 7-17

**7-2.** A D flip-flop has these specifications:

$$t_{\text{setup}} = 10 \text{ ns}$$

$$t_{\rm hold} = 5 \, \rm ns$$

$$t_p = 30 \, \text{ns}$$

- a. How far ahead of the rising clock edge must the data bit be applied to the *D* input to ensure correct storage?

- b. After the rising clock edge, how long must you wait before letting the data bit change?

- c. How long after the rising clock edge will Q change?

Fig. 7-18

Fig. 7-19

Fig. 7-20

Fig. 7-21

Fig. 7-22

**7-3.** In Fig. 7-18, the data word to be stored is

$$S = 1001$$

- a. If LOAD is low, what does Q equal after the positive clock edge?

- b. If LOAD is high, what does Q equal after the positive clock edge.

- **7-4.** The clock of Fig. 7-19 has a frequency of 1 MHz, and the flip-flop has a propagation delay time of 25 ns.

- a. What is the period of the clock?

- b. The frequency of the Q output? Its period?

- c. How long after the negative clock edge does the *Q* output change?

- **7-5.** The clock has a frequency of 6 MHz in Fig. 7-19. What is the frequency of the *Q* output? This circuit is sometimes called a divide-by-2 circuit. Explain why.

- **7-6.** In Fig. 7-20, *CLR* is taken low temporarily, then high. Draw the timing diagram. If the clock has a frequency of 1 MHz, what is the frequency of the *Q* output? Is this a divide-by-2 circuit?

- 7-7. Figure 7-21 shows a NAND latch used as a switch debouncer. With the switch in the STOP position, what do Q and Y equal? If the switch is thrown to the START position, what do Q and Y equal?

- **7-8.** The clock has a frequency of 1 MHz in Fig. 7-22. With the switch in the OFF position, what is the frequency of the Q output? If the switch is thrown to the ON position, what is the frequency of the Q output?

# **REGISTERS AND COUNTERS**

A register is a group of memory elements that work together as a unit. The simplest registers do nothing more than store a binary word; others modify the stored word by shifting its bits left or right or by performing other operations to be discussed in this chapter. A counter is a special kind of register, designed to count the number of clock pulses arriving at its input. This chapter discusses some basic registers and counters used in microcomputers.

## 8-1 BUFFER REGISTERS

A buffer register is the simplest kind of register; all it does is store a digital word.

#### Basic Idea

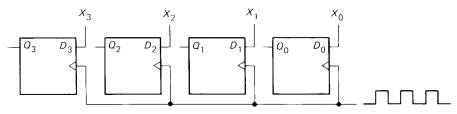

Figure 8-1 shows a buffer register built with positive-edge-triggered D flip-flops. The X bits set up the flip-flops for loading. Therefore, when the first positive clock edge arrives, the stored word becomes  $Q_3Q_2Q_1Q_0 = X_3X_2X_1X_0$ . In chunked notation,

$$\mathbf{O} = \mathbf{X}$$

The circuit is too primitive to be of any use. What it needs is some control over the *X* bits, some way of holding them off until we're ready to store them.

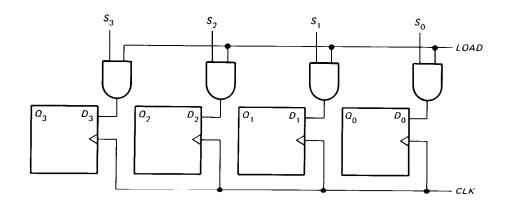

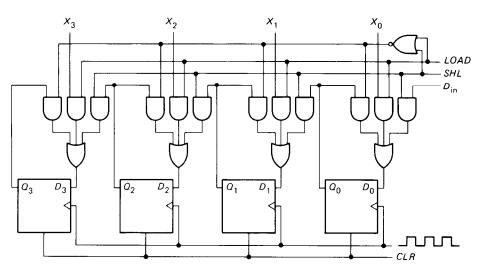

## Controlled

Figure 8-2 is more like it. This is a controlled buffer register with an active-high *CLR*. Therefore, when *CLR* goes high, all flip-flops reset and the stored word becomes

$$\mathbf{O} = 0000$$

When *CLR* returns low, the register is ready for action. *LOAD* is a control input; it determines what the circuit does. When *LOAD* is low, the *X* bits cannot reach the flip-

flops. At the same time, the inverted signal  $\overline{LOAD}$  is high; this forces each flip-flop output to feed back to its data input. When each rising clock edge arrives, data is circulated or retained. In other words, the register contents are unchanged when LOAD is low.

When *LOAD* goes high, the *X* bits are transmitted to the data inputs. After a short setup time, the flip-flops are ready for loading. With the arrival of the positive clock edge, the *X* bits are loaded and the stored word becomes

$$Q_3Q_2Q_1Q_0 = X_3X_2X_1X_0$$

If LOAD returns to low, the foregoing word is stored indefinitely; this means that the X bits can change without affecting the stored word.

## EXAMPLE 8-1

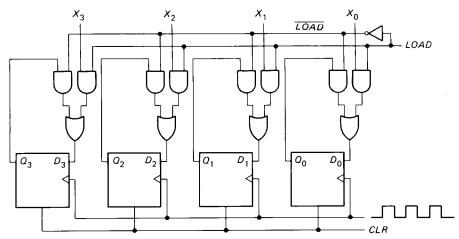

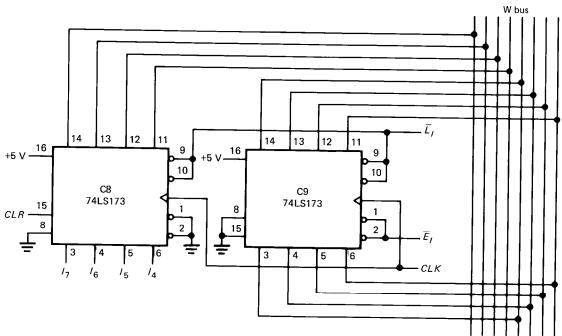

Chapter 10 discusses the *SAP* (simple-as-possible) computer. This educational computer has three generations, SAP-1, SAP-2, and SAP-3. Figure 8-3 shows the output register of the SAP-1 computer. The 74LS173 chips are controlled buffer registers, similar to Fig. 8-2. What does the circuit do?

## SOLUTION

To begin with, it is an 8-bit buffer register built with TTL chips. Each chip handles 4 bits of input word X. The upper nibble  $X_7X_6X_5X_4$  goes to pins 14, 13, 12, and 11 of C22; the lower nibble  $X_3X_2X_1X_0$  goes to pins 14, 13, 12, and 11 of the C23.

Output word  $\mathbf{Q}$  drives an 8-bit LED display. The upper nibble  $Q_7Q_6Q_5Q_4$  comes out of pins 3, 4, 5, and 6 of C22; the lower nibble  $Q_3Q_2Q_1Q_0$  comes out of pins 3, 4, 5, and 6 of C23. The typical high-state output of a 74LS173 is 3.5 V, and the typical LED drop is 1.5 V. Since each current-limiting resistance is 1 k $\Omega$ , the high-state current is approximately 2 mA for each output pin.

Fig. 8-1 Buffer register.

Fig. 8-2 Controlled buffer register.

Fig. 8-3 SAP-1 output register.

The 74LS173 requires a 5-V supply for pin 16 and a ground return on pin 8. The SAP-1 output register never needs clearing; this is why the CLR input (pin 15) is made inactive by tying it to ground. In a 74LS173, pins 9 and 10 are separate *LOAD* controls. Because SAP-1 needs only a single *LOAD* control, pins 9 and 10 are tied together. The bubbles on pins 9 and 10 indicate an active low state; this means that *LOAD* must be low for the positive clock

edge to store the input word. See Appendix 4 for a more detailed description of the 74LS173.

The action of the circuit is straightforward. While *LOAD* is high, the register contents are unchanged even though the clock is running. To change the stored word, *LOAD* must go low. Then the next rising clock edge loads the *X* bits into the register. As soon as this happens, the LED display shows the new contents.

## 8-2 SHIFT REGISTERS

A shift register moves the stored bits left or right. This bit shifting is essential for certain arithmetic and logic operations used in microcomputers.

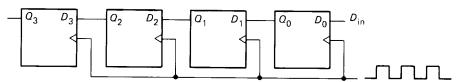

#### Shift Left

Figure 8-4 is a *shift-left* register. As shown,  $D_{in}$  sets up the right flip-flop,  $Q_0$  sets up the second flip-flop,  $Q_1$  the third, and so on. When the next positive clock edge strikes, therefore, the stored bits move one position to the left.

As an example, here's what happens with  $D_{in} = 1$  and

$$\mathbf{O} = 0000$$

All data inputs except the one on the right are 0s. The arrival of the first rising clock edge sets the right flip-flop, and the stored word becomes

$$Q = 0001$$

This new word means  $D_1$  now equals 1, as well as  $D_0$ . When the next positive clock edge hits, the  $Q_1$  flip-flop sets and the register contents become

$$0 = 0011$$

The third positive clock edge results in

$$Q = 0111$$

and the fourth rising clock edge gives

$$Q = 1111$$

Hereafter, the stored word is unchanged as long as  $D_{\rm in} = 1$ .

Suppose  $D_{in}$  is now changed to 0. Then, successive clock pulses produce these register contents:

Q = 1110 Q = 1100 Q = 1000

Q = 0000

As long as  $D_{in} = 0$ , subsequent clock pulses have no further effect.

The timing diagram of Fig. 8-5 summarizes the foregoing discussion.

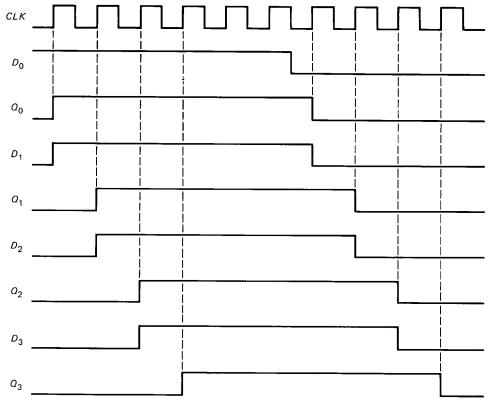

### Shift Right

Figure 8-6 is a shift-right register. As shown, each O output sets up the D input of the preceding flip-flop. When the rising clock edge arrives, the stored bits move one position to the right.

Here's an example with  $D_{in} = 1$  and

$$Q = 0000$$

All data inputs except the one on the left are 0s. The first positive clock edge sets the left flip-flop and the stored word becomes

$$Q = 1000$$

With the appearance of this word,  $D_3$  and  $D_2$  are 1s. The second rising clock edge gives

$$0 = 1100$$

The third clock pulse gives

$$Q = 1110$$

and the fourth clock pulse gives

$$Q = 1111$$

## 8-3 CONTROLLED SHIFT REGISTERS

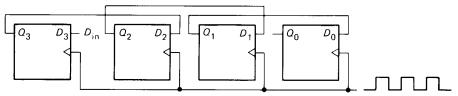

A controlled shift register has control inputs that determine what it does on the next clock pulse.

## **SHL Control**

Figure 8-7 shows how the shift-left operation can be controlled. SHL is the control signal. When SHL is low, the inverted signal SHL is high. This forces each flip-flop output to feed back to its data input. Therefore, the data is retained in each flip-flop as the clock pulses arrive. In this way, a digital word can be stored indefinitely.

When SHL goes high,  $D_{in}$  sets up the right flip-flop,  $Q_0$ sets up the second flip-flop,  $Q_1$  the third flip-flop, and so on. In this mode, the circuit acts like a shift-left register. Each positive clock edge shifts the stored bits one position to the left.

#### Serial Loading

Serial loading means storing a word in the shift register by entering 1 bit per clock pulse. To store a 4-bit word, we need four clock pulses. For instance, here's how to serially store the word

$$X = 1010$$

With SHL high in Fig. 8-7, make  $D_{in} = 1$  for the first clock pulse,  $D_{in} = 0$  for the second clock pulse,  $D_{in} = 1$

Fig. 8-4 Shift-left register.

Fig. 8-5 Shift-left timing diagram.

Fig. 8-6 Shift-right register.

Fig. 8-7 Controlled shift register.

for the third clock pulse, and  $D_{\rm in}=0$  for the fourth clock pulse. If the register is clear before the first clock pulse, the successive register contents look like this:

| $\mathbf{Q} = 0001$ | $(D_{\rm in} = 1: \text{first clock pulse})$   |

|---------------------|------------------------------------------------|

| $\mathbf{Q} = 0010$ | $(D_{\rm in} = 0: second clock pulse)$         |

| $\mathbf{Q} = 0101$ | $(D_{in} = 1: third clock pulse)$              |

| $\mathbf{Q} = 1010$ | $(D_{\rm in} = 0: \text{ fourth clock pulse})$ |

In this way, data is entered serially into the right end of the register and shifted left until all 4 bits have been stored. After the last bit is entered, *SHL* is taken low to freeze the register contents.

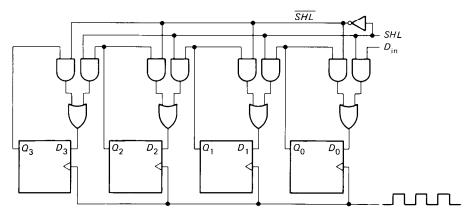

## Parallel Loading

Figure 8-8 is another step in the evolution of shift registers. The circuit can load X bits directly into the flip-flops, the same as a buffer register. This kind of entry is called parallel or broadside loading; it takes only one clock pulse to store a digital word.

If *LOAD* and *SHL* are low, the output of the NOR gate is high and flip-flop outputs return to their data inputs. This forces the data to be retained in each flip-flop as the positive clock edges arrive. In other words, the register is inactive when *LOAD* and *SHL* are low, and the contents are stored indefinitely.

When *LOAD* is low and *SHL* is high, the circuit acts like a shift-left register, as previously described. On the other hand, when *LOAD* is high and *SHL* is low, the circuit acts like a buffer register because the *X* bits set up the flip-flops for broadside loading. (Having *LOAD* and *SHL* simultaneously high is forbidden because it's impossible to do both operations on a single clock edge.)

By adding more flip-flops we can build a controlled shift register of any length. And with more gates, the shift-right operation can be included. As an example, the 74198 is a TTL 8-bit bidirectional shift register. It can broadside load, shift left, or shift right.

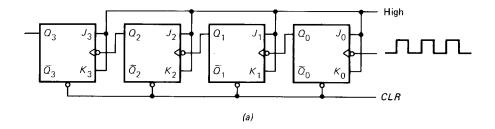

## **8-4 RIPPLE COUNTERS**

A *counter* is a register capable of counting the number of clock pulses that have arrived at its clock input. In its simplest form it is the electronic equivalent of a binary odometer.

#### The Circuit

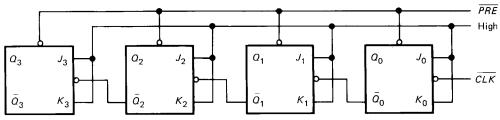

Figure 8-9a shows a counter built with JK flip-flops. Since the J and K inputs are returned to a high voltage, each flip-flop will toggle when its clock input receives a negative edge.

Here's how the counter works. Visualize the Q outputs as a binary word

$$\mathbf{Q} = \mathbf{Q}_3 \mathbf{Q}_2 \mathbf{Q}_1 \mathbf{Q}_0$$

$Q_3$  is the most significant bit (MSB), and  $Q_0$  is the least significant bit (LSB). When *CLR* goes low; all flip-flops reset. This results in a digital word of

$$\mathbf{O} = 0000$$

When CLR returns to high, the counter is ready to go. Since the LSB flip-flop receives each clock pulse,  $Q_0$  toggles once per negative clock edge, as shown in the timing diagram of Fig. 8-9b. The remaining flip-flops toggle less often because they receive their negative edges from the preceding flip-flops.

For instance, when  $Q_0$  goes from 1 back to 0, the  $Q_1$  flip-flop receives a negative edge and toggles. Likewise,

Fig. 8-8 Shift register with broadside load.

Fig. 8-9 (a) Ripple counter; (b) timing diagram.

when  $Q_1$  changes from 1 back to 0, the  $Q_2$  flip-flop gets a negative edge and toggles. And when  $Q_2$  goes from 1 to 0, the  $Q_3$  flip-flop toggles. In other words, whenever a flip-flop resets to 0, the next higher flip-flop toggles (see Fig. 8-9b).

What does this remind you of? Reset and carry! Each flip-flop acts like a wheel in a binary odometer; whenever it resets to 0, it sends a carry to the next higher flip-flop. Therefore, the counter of Fig. 8-9a is the electronic equivalent of a binary odometer.

## Counting

If *CLR* goes low then high, the register contents of Fig. 8-9a become

$$\mathbf{Q} = 0000$$

When the first clock pulse hits the LSB flip-flop,  $Q_0$  becomes a 1. So the first output word is

$$Q = 0001$$

When the second clock pulse arrives,  $Q_0$  resets and carries; therefore, the next output word is

$$\mathbf{Q} = 0010$$

The third clock pulse advances  $Q_0$  to 1; this gives

$$Q = 0011$$

The fourth clock pulse forces the  $Q_0$  flip-flop to reset and carry. In turn, the  $Q_1$  flip-flop resets and carries. The resulting output word is

$$\mathbf{Q} = 0100$$

The fifth clock pulse gives

$$Q = 0101$$

The sixth gives

$$\mathbf{Q} = 0110$$

and the seventh gives

$$\mathbf{Q} = 0111$$

On the eighth clock pulse,  $Q_0$  resets and carries,  $Q_1$  resets and carries,  $Q_2$  resets and carries, and  $Q_3$  advances to 1. So the output word becomes

$$\mathbf{O} = 1000$$

The ninth clock pulse gives

$$\mathbf{O} = 1001$$

The tenth gives

$$Q = 1010$$

and so on.

TABLE 8-1. RIPPLE COUNTER

| Count  | $Q_3$ | $\mathbf{Q}_2$ | $\mathbf{Q}_1$ | $Q_0$ |

|--------|-------|----------------|----------------|-------|

| 0      | 0     | 0              | 0              | 0     |

| 1      | 0     | 0              | 0              | 1     |

| 2      | 0     | 0              | 1              | 0     |

| 3      | 0     | 0              | 1              | 1     |

| 4<br>5 | 0     | 1              | 0              | 0     |

| 5      | 0     | 1              | 0              | 1     |

| 6      | 0     | 1              | 1              | 0     |

| 7      | 0     | 1              | 1              | 1     |

| 8      | 1     | 0              | 0              | 0     |

| 9      | 1     | 0              | 0              | 1     |

| 10     | 1     | 0              | 1              | 0     |

| 11     | 1     | 0              | 1              | 1     |

| 12     | 1     | 1              | 0              | 0     |

| 13     | 1     | 1              | 0              | 1     |

| 14     | 1     | 1              | 1              | 0     |

| 15     | 1     | 1              | 1              | 1     |

The last word is

$$Q = 1111$$

corresponding to the fifteenth clock pulse. The next clock pulse resets all flip-flops. Therefore, the counter resets to

$$\mathbf{O} = 0000$$

and the cycle repeats.

Table 8-1 summarizes the operation of the counter. *Count* represents the number of clock pulses that have arrived. As you see, the counter output is the binary equivalent of the decimal count.

## **Frequency Division**

Each flip-flop in Fig. 8-9a divides the clock frequency by a factor of 2. This is why a flip-flop is sometimes called a *divide-by-2 circuit*. Since each flip-flop divides the clock frequency by 2, n flip-flops divide the clock frequency by  $2^n$ .

The timing diagram of Fig. 8-9b illustrates the divideby-2 action.  $Q_0$  is one-half the clock frequency,  $Q_1$  is onefourth the clock frequency,  $Q_2$  is one-eighth the clock frequency, and  $Q_3$  is one-sixteenth of the clock frequency. In other words,

- 1 flip-flop divides by 2

- 2 flip-flops divide by 4

- 3 flip-flops divide by 8

- 4 flip-flops divide by 16

and

n flip-flops divide by  $2^n$

## Ripple Counter

The counter of Fig. 8-9a is known as a *ripple counter* because the carry moves through the flip-flops like a ripple on water. In other words, the  $Q_0$  flip-flop must toggle before the  $Q_1$  flip-flop, which in turn must toggle before the  $Q_2$  flip-flop, which in turn must toggle before the  $Q_3$  flip-flop. The worst case occurs when the stored word changes from 0111 to 1000, or from 1111 to 0000. In either case, the carry has to move all the way to the MSB flip-flop. Given a  $t_p$  of 10 ns per flip-flop, it takes 40 ns for the MSB to change.

By adding more flip-flops to the left end of Fig. 8-9a we can build a ripple counter of any length. Eight flip-flops give an 8-bit ripple counter, twelve flip-flops result in a 12-bit ripple counter, and so on.

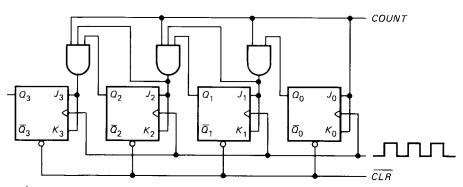

## **Controlled Counter**

A controlled counter counts clock pulses only when commanded to do so. Figure 8-10 shows how it's done. The *COUNT* signal can be low or high. Since it conditions the *J* and *K* inputs, *COUNT* controls the action of the counter, forcing it to either do nothing or to count clock pulses.

When COUNT is low, the J and K inputs are low; therefore, all flip-flops remain latched in spite of the clock pulses driving the counter.

On the other hand, when *COUNT* is high, the *J* and *K* inputs are high. In this case, the counter works as previously described; each negative clock edge increments the stored count by 1.

#### EXAMPLE 8-2

As mentioned earlier, the program and data are stored in the memory before a computer run. The program is a list of instructions telling the computer how to process the data.

Fig. 8-10 Controlled ripple counter.

Fig. 8-11 SAP-1 program counter.

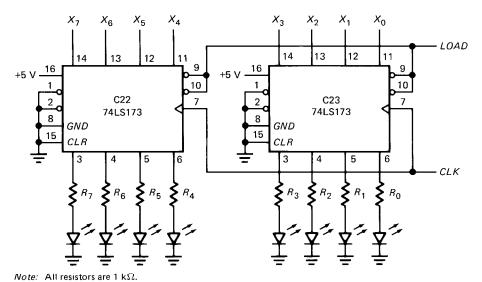

Every microcomputer has a *program counter* to keep track of the instruction being executed.

Figure 8-11 shows part of the program counter used in SAP-1. What does it do?

## **SOLUTION**

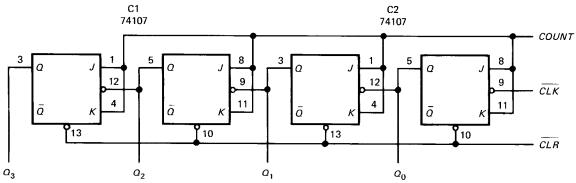

To begin with, let's find out why the  $\overline{CLR}$  and  $\overline{CLK}$  signals are shown as complements. Signals are often available in complemented and uncomplemented form. The switch debouncer of Fig. 7-4a has two outputs, CLR and  $\overline{CLR}$ . In SAP-1 the CLR signal goes to any circuit that uses an active high clear and the  $\overline{CLR}$  signal to any circuit with an active low clear. This is why  $\overline{CLR}$  goes to the counter of Fig. 8-11; it has an active low clear. A similar idea applies to the clock signal.

The 74107 is a dual JK master-slave flip-flop. The SAP-1 program counter uses two 74107s. Although not shown, pin 14 ties to the 5-V supply, and pin 7 is the chip ground. Because master-slave flip-flops are used, a high  $\overline{CLK}$  cocks the master and a low  $\overline{CLK}$  triggers the slave.

Before a computer run, the operator pushes a clear button that sends a low  $\overline{CLR}$  to the program counter. This resets its count to

$$\mathbf{Q} = 0000$$

When the operator releases the button,  $\overline{CLR}$  goes high and the computer run begins.

After the first instruction has been fetched from the memory, *COUNT* goes high for one clock pulse and the count becomes

$$\mathbf{O} = 0001$$

This count indicates that the first instruction has been fetched from the memory. (Later you will see how the computer executes the first instruction.)

After the first instruction has been executed, the computer fetches the second instruction in the memory. Once again,

COUNT goes high for one clock pulse, producing a new count of

$$Q = 0010$$

The program counter now indicates that the second instruction has been fetched from the memory.

Each time a new instruction is fetched from the memory, the program counter is incremented to produce the next higher count. In this way, the computer can keep track of which instruction it's working on.

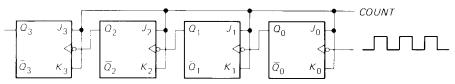

## 8-5 SYNCHRONOUS COUNTERS

When the carry has to propagate through a chain of n flip-flops, the overall propagation delay time is  $nt_p$ . For this reason ripple counters are too slow for some applications. To get around the ripple-delay problem, we can use a synchronous counter.

#### The Circuit

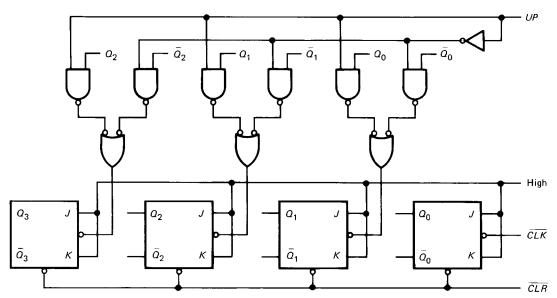

Figure 8-12 shows one way to build a synchronous counter with positive-edge-triggered flip-flops. This time, clock pulses drive all flip-flops in parallel. Because of the simultaneous clocking, the correct binary word appears after one propagation delay time rather than four.

The least significant flip-flop has its J and K inputs tied to a high voltage; therefore, it responds to each positive clock edge. But the remaining flip-flops can respond to the positive clock edge only under certain conditions. As shown in Fig. 8-12, the  $Q_1$  flip-flop toggles on the positive clock edge only when  $Q_0$  is a 1. The  $Q_2$  flip-flop toggles only when  $Q_1$  and  $Q_0$  are 1s. And the  $Q_3$  flip-flop toggles only when  $Q_2$ ,  $Q_1$ , and  $Q_0$  are 1s. In other words, a flip-flop toggles on the next positive clock edge if all lower bits are 1s.

Fig. 8-12 Synchronous counter.

Here's the counting action. A low  $\overline{CLR}$  resets the counter to

$$Q = 0000$$

When the  $\overline{CLR}$  line goes high, the counter is ready to go. The first positive clock edge sets  $Q_0$  to get

$$Q = 0001$$

Since  $Q_0$  is now 1, the  $Q_1$  flip-flop is conditioned to toggle on the next positive clock edge.

When the second positive clock edge arrives,  $Q_1$  and  $Q_0$  simultaneously toggle and the output word becomes

$$\mathbf{Q} = 0010$$

The third positive clock edge advances the count by 1:

$$Q = 0011$$

Because  $Q_1$  and  $Q_0$  are now 1s, the  $Q_2$ ,  $Q_1$ , and  $Q_0$  flip-flops are conditioned to toggle on the next positive clock edge. When the fourth positive clock edge arrives,  $Q_2$ ,  $Q_1$ , and  $Q_0$  toggle simultaneously, and after one propagation delay time the output word becomes

$$Q = 0100$$

The successive  $\mathbf{Q}$  words are 0101, 0110, 0111, and so on up to 1111 (equivalent to decimal 15). The next positive clock edge resets the counter, and the cycle repeats.

By adding more flip-flops and gates we can build synchronous counters of any length. The advantage of a synchronous counter is its speed; it takes only one propagation delay time for the correct binary count to appear after the clock edge hits.

#### **Controlled Counter**

Figure 8-13 shows how to build a *controlled synchronous* counter. A low COUNT disables all flip-flops. When COUNT is high, the circuit becomes a synchronous counter; each positive clock edge advances the count by 1.

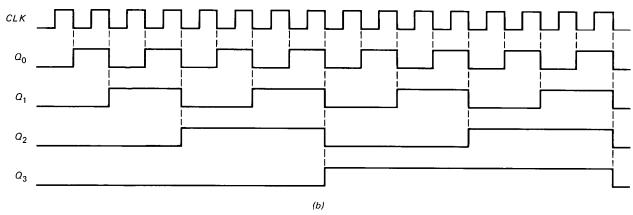

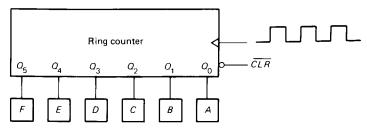

## 8-6 RING COUNTERS

Instead of counting with binary numbers, a *ring counter* uses words that have only a single high bit.

#### Circuit

Figure 8-14 is a *ring counter* built with D flip-flops. The  $Q_0$  output sets up the  $D_1$  input, the  $Q_1$  output sets up the  $D_2$  input, and so on. Therefore, a ring counter resembles a

Fig. 8-13 Controlled synchronous counter.

Fig. 8-14 Ring counter.

shift-left register because the bits are shifted left one position per positive clock edge. But the circuit differs because the final output is fed back to the  $D_0$  input. This kind of action is called *rotate left*; bits are shifted left and fed back to the input.

When  $\overline{CLR}$  goes low then back to high, the initial output word is

$$Q = 0001$$

The first positive clock edge shifts the MSB into the LSB position; the other bits shift left one position. Therefore, the output word becomes

$$Q = 0010$$

The second positive clock edge causes another rotate left and the output word changes to

$$\mathbf{Q} = 0100$$

After the third positive clock edge, the output word is

$$\mathbf{O} = 1000$$

The fourth positive clock edge starts the cycle over because the rotate left produces

$$Q = 0001$$

The stored 1 bit follows a circular path, moving left through the flip-flops until the final flip-flop sends it back to the first flip-flop. This is why the circuit is called a ring counter.

#### **More Bits**

Add more flip-flops and you can build a ring counter of any length. With six flip-flops we get a 6-bit ring counter. Again, the  $\overline{CLR}$  signal resets all flip-flops except the LSB flip-flop. Therefore, the successive ring words are

| $\mathbf{Q} = 000001$ | (0) |

|-----------------------|-----|

| $\mathbf{Q} = 000010$ | (1) |

| $\mathbf{Q} = 000100$ | (2) |

| $\mathbf{Q} = 001000$ | (3) |

| $\mathbf{Q} = 010000$ | (4) |

| $\mathbf{Q} = 100000$ | (5) |

Each of the foregoing words has only 1 high bit. The initial word stands for decimal 0 and the final word for decimal 5. If a ring counter has n flip-flops, therefore, the final ring word represents decimal n-1.

## **Applications**

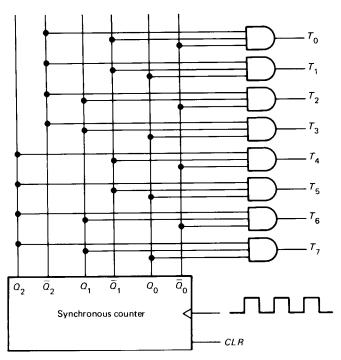

Ring counters cannot compete with ripple and synchronous counters when it comes to ordinary counting, but they are invaluable when it's necessary to control a sequence of operations. Because each ring word has only 1 high bit, you can activate one of several devices.

For instance, suppose the six small boxes (A to F) of Fig. 8-15 are digital circuits that can be turned on by a high Q bit. When  $\overline{CLR}$  goes low,  $Q_0$  goes high and activates device A. After  $\overline{CLR}$  returns to high, successive clock pulses turn on each device for a short time. In other words, as the stored 1 bit shifts left, it turns on B to F in sequence, and then the cycle starts over.

Many digital circuits participate during a computer run. To fetch and execute instructions, a computer has to activate

Fig. 8-15 Controlling a sequence of operations

Note: Pin 14 is connected to +5 V, and pin 7 is grounded.

Fig. 8-16 SAP-1 ring counter.

these circuits at precisely the right time and in the right sequence. This is where ring counters shine; they produce the ring words for timing different operations during a computer run.

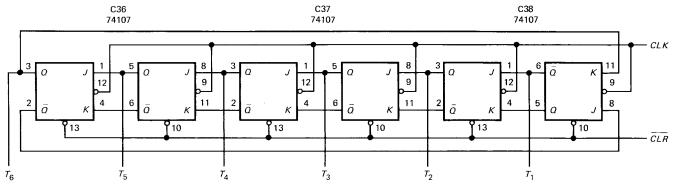

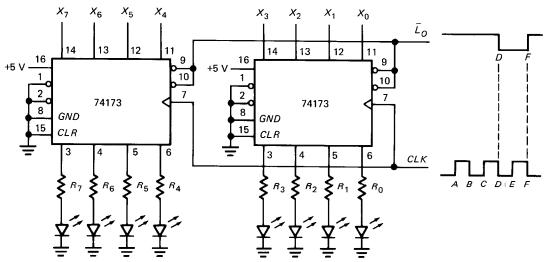

#### EXAMPLE 8-3

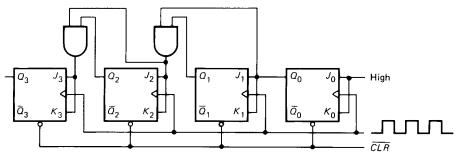

Figure 8-16 shows the ring counter used in the SAP-1 computer.  $T_6$  to  $T_1$  are called *timing* signals because they control a sequence of digital operations. What does this ring counter do?

#### SOLUTION

The 74107 is a dual JK master-slave flip-flop, previously used in the SAP-1 program counter (Example 8-2). The flip-flops are connected in a rotate-left mode. Since the 74107 does not have a preset input, the  $Q_0$  flip-flop is inverted so that its  $\overline{Q}$  output drives the J input of the  $Q_1$  flip-flop. In this way, a low  $\overline{CLR}$  produces the initial timing word

$$T_6T_5T_4T_3T_2T_1 = 000001$$

In chunked form

T = 000001

Because of the master-slave action, a complete clock pulse is needed to produce the next ring word. After  $\overline{CLR}$  returns high, the successive clock pulses produce the timing words

T = 000010

T = 000100

$\mathbf{T} = 001000$

$\mathbf{T} = 010000$

T = 100000

Then the cycle repeats.

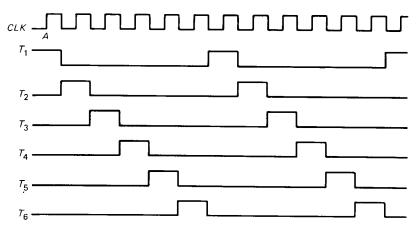

#### EXAMPLE 8-4

The clock frequency in Fig. 8-16 is 1 kHz. *CLR* goes low then high. Show the timing diagram.

#### SOLUTION

Figure 8-17 is the timing diagram. Since the clock has a frequency of 1 kHz, it has a period of 1 ms. This is the amount of time between successive negative clock edges. Each negative clock edge produces the next ring word. When its turn comes, each timing signal goes high for 1 ms.

Notice that the CLK signal of Fig. 8-17 is the input to the ring counter of Fig. 8-16, whereas the complement  $\overline{CLK}$  is the input to the program counter of Fig. 8-11. This half-cycle difference is deliberate. The reason is given in Chap. 10, which explains how the timing signals of Fig. 8-17 control circuits that fetch and execute each program instruction.

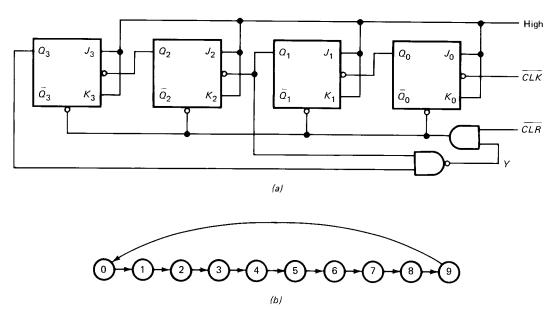

## 8-7 OTHER COUNTERS

The *modulus* of a counter is the number of output states it has. A 4-bit ripple counter has a modulus of 16 because it has 16 distinct states numbered from 0000 to 1111. By changing the design we can produce a counter with any desired modulus.

## **Mod-10 Counter**

Figure 8-18a shows a way to build a modulus-10 (or mod-10) counter. The circuit counts from 0000 to 1001, as before. However, on the tenth clock pulse, the counter

Fig. 8-17 SAP-1 clock and timing pulses.

Fig. 8-18 Mod-10 counter.

generates its own clear signal and the count jumps back to 0000. In other words, the count sequence is

$$\begin{array}{lll} \mathbf{Q} = 0000 & (0) \\ \mathbf{Q} = 0001 & (1) \\ \mathbf{Q} = 0010 & (2) \\ \mathbf{Q} = 0011 & (3) \\ \mathbf{Q} = 0100 & (4) \\ \mathbf{Q} = 0101 & (5) \\ \mathbf{Q} = 0110 & (6) \\ \mathbf{Q} = 0111 & (7) \\ \mathbf{Q} = 1000 & (8) \\ \mathbf{Q} = 1001 & (9) \\ \mathbf{Q} = 0000 & (0) \end{array}$$

As you see, the circuit skips states 10 to 15 (1010 through 1111). The counting sequence is summarized by the *state diagram* of Fig. 8-18b.

Why does the counter skip the states from 10 to 15? Because of the AND gate, the counter can be reset by a low  $\overline{CLR}$  or a low Y. Initially,  $\overline{CLR}$  goes low to produce

$$\mathbf{Q} = 0000$$

When  $\overline{CLR}$  returns to high, the counter is ready for action. The output of the NAND gate is

$$Y = \overline{Q_3Q_1}$$

This output is high for the first nine states (0000 to 1001). Nothing unusual happens when the circuit is counting from 0 to 9. On the tenth clock pulse, however, the **Q** word becomes

$$Q = 1010$$

which means that  $Q_3$  and  $Q_1$  are high. Almost immediately, Y goes low, forcing the counter to reset to

$$Q = 0000$$

Y then goes high, and the counter is ready to start over.

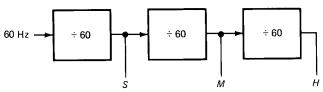

Since it takes 10 clock pulses to reset the counter, the output frequency of the  $Q_3$  flip-flop is one-tenth of the clock frequency. This is why a mod-10 counter is also known as a *divide-by-10 circuit*.

A mod-10 counter like Fig. 8-18a is often called a *decade* counter. Because it counts from 0 to 9, it is a natural choice in BCD applications like frequency counters, digital voltmeters, and electronic wristwatches.

To get any other modulus, we can use the same basic idea. For instance, to get a mod-12 counter, we can drive the NAND gate of Fig. 8-18a with  $Q_3$  and  $Q_2$ . Then the circuit counts from 0 to 11 (0000 to 1011). On the next clock pulse,  $Q_3$  and  $Q_2$  are high, which clears the counter. (What is the modulus if  $Q_3$  and  $Q_0$  drive the NAND gate?)

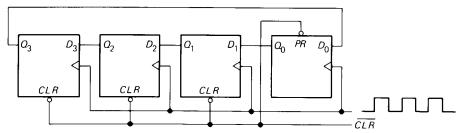

#### **Down Counter**

All the counters discussed so far have counted upward, toward higher numbers. Figure 8-19 shows a *down counter*; it counts from 1111 to 0000. Each flip-flop toggles when its clock input goes from 1 to 0. This is equivalent to an uncomplemented output going from 0 to 1. For instance, the  $Q_1$  flip-flop toggles when  $\overline{Q}_0$  goes from 1 to 0; this is equivalent to  $Q_0$  going from 0 to 1.

A preset signal generated elsewhere is available in either uncomplemented or complemented form; PRE goes to all circuits with an active-high preset;  $\overline{PRE}$  goes to all circuits with an active-low preset. Initially, the preset signal  $\overline{PRE}$  goes low in Fig. 8-19, producing an output word of

$$\mathbf{O} = 1111 \quad (15)$$

When  $\overline{PRE}$  goes high, the action starts. Notice that  $Q_0$  toggles once per clock pulse. In the following discussion, a *positive toggle* means a change from 0 to 1, a *negative toggle* means a change from 1 to 0.

The first clock pulse produces a negative toggle in  $Q_0$ ; nothing else happens:

$$\mathbf{Q} = 1110 \qquad (14)$$

The second clock pulse produces a positive toggle in  $Q_0$ , which produces a negative toggle in  $Q_1$ :

$$\mathbf{Q} = 1101 \tag{13}$$

On the third clock pulse,  $Q_0$  toggles negatively, and

$$\mathbf{Q} = 1100 \qquad (12)$$

On the fourth clock pulse,  $Q_0$  toggles positively,  $Q_1$  toggles positively, and  $Q_2$  toggles negatively:

$$Q = 1011$$

(11)

You should have the idea by now. The circuit is counting down, from 15 to 0. When it reaches 0,

$$\mathbf{Q} = 0000$$

On the next clock pulse, all flip-flops toggle positively to get

$$Q = 1111$$

and the cycle repeats.

## **Up-Down Counter**

Figure 8-20 shows how to build an *up-down counter*. The flip-flop outputs are connected to *steering* networks. An *UP* control signal produces either down counting or up counting. If the *UP* signal is low,  $\overline{Q}_2$ ,  $\overline{Q}_1$ , and  $\overline{Q}_0$  are transmitted to the clock inputs; this results in a down counter. On the other hand, when *UP* is high,  $Q_2$ ,  $Q_1$ , and  $Q_0$  drive the clock inputs and the circuit becomes an up counter.

#### **Presettable Counter**

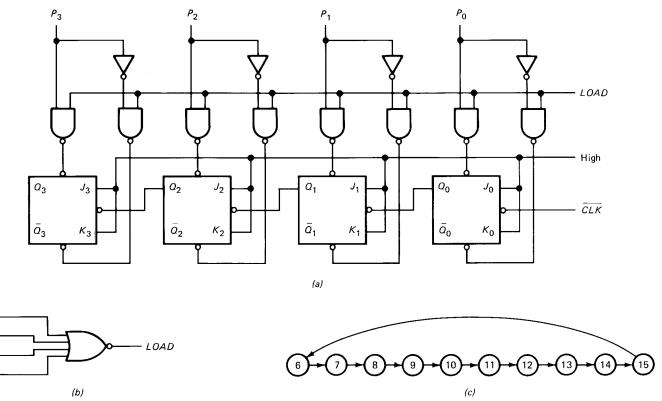

In a presettable counter, the count starts at a number greater than zero. Figure 8-21a shows a presettable counter; the count begins with P<sub>3</sub>P<sub>2</sub>P<sub>1</sub>P<sub>0</sub>, a number between 0000 and 1111.

To start the analysis, look at the *LOAD* control line. When it is low, all NAND gates have high outputs; therefore,

Fig. 8-19 Down counter.

Fig. 8-20 Up-down counter.

Fig. 8-21 Presettable counter.

the preset and clear inputs of all flip-flops are inactive. In this case, the circuit counts upward, as previously described. The data inputs  $P_3$  to  $P_0$  have no effect because the NAND gates are disabled.

When the LOAD line is high, the data inputs and their complements pass through the NAND gates and preset the

counter to  $P_3P_2P_1P_0$ . As an example, suppose the preset input is

$$P_3P_2P_1P_0 = 0110$$

Because of the two left NAND gates, the low  $P_3$  produces a high preset and a low clear for the  $Q_3$  flip-flop; this clears

$Q_3$  to a 0. By a similar argument, the high  $P_2$  sets  $Q_2$ , the high  $P_1$  sets  $Q_1$ , and the low  $P_0$  clears  $Q_0$ . Therefore, the counter is preset to

$$Q = 0110$$

When *LOAD* returns to low, the circuit reverts to a counter. Successive clock pulses produce

$$Q = 0111$$

$Q = 1000$

$Q = 1001$

up to a maximum count of

$$Q = 1111$$

The next clock pulse resets the counter to

$$\mathbf{O} = 0000$$

In summary,

- 1. When LOAD is low, the circuit counts.

- 2. When LOAD is high, the counter presets to  $P_3P_2P_1P_0$ .

## **Programmable Modulus**

The most important use of a presettable counter is *programming a modulus*. Here's the idea. Let's add the NOR gate of Fig. 8-21b to the presettable counter of Fig. 8-21a. Then the Q outputs drive the NOR gate, and the NOR gate controls the LOAD line of the presettable counter. Because a NOR gate recognizes a word with all 0s and disregards all others, LOAD is high for Q = 0000 and low for all other words. This means that the circuit presets when Q = 0000 and counts when Q is 0001 to 1111.

If the preset input is 0110, successive clock pulses produce 0111, 1000, 1001, . . . , reaching a maximum value of

$$\mathbf{O} = 1111$$

The next clock pulse resets the count to

$$\mathbf{Q} = 0000$$

Almost immediately, however, the NOR-gate outputs goes high, and the data inputs preset the counter to

$$Q = 0110$$

In other words, the counter effectively skips states 0 to 5, illustrated by the state diagram of Fig. 8-21c.

Figure 8-21c shows 10 distinct states; by presetting 0110, we have programmed the counter to become a mod-10

counter. If we change the preset input, we get a different modulus. In general,

$$M = N - P \tag{8-1}$$

where M = modulus of preset counter

N =natural modulus

P =preset count

The natural modulus equals  $2^n$  where n is the number of flip-flops in the counter. So four flip-flops give a natural modulus of 16, eight give a natural modulus of 256, and so on.

As an example, if you preset 82 into a preset counter with eight flip-flops, the modulus is

$$M = 256 - 82 = 174$$

In other words, this preset counter is equivalent to a divideby-174 circuit.

#### **TTL Counters**

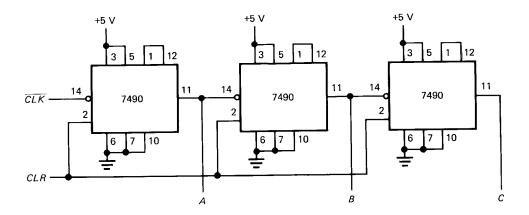

Table 8-2 lists some TTL counters. The 7490 is an industry standard, a widely used decade counter. This ripple counter has two sections, a divide-by-2 and a divide-by-5. This allows you to divide by 2, to divide by 5, or to cascade both sections to divide by 10.

The 7492 is a mod-12 ripple counter, organized in two sections by divide-by-2 and divide-by-6. This allows you to divide by 2, divide by 6, or cascade to divide by 12. The 7493 is a mod-16 ripple counter, with two sections of divide-by-2 and divide-by-8.

The 74160 and 74161 are presettable synchronous counters, the first being a decade counter and the second a divide-by-16 counter. Finally, the 74190 and 74191 are up-down presettable counters.

This is a sample of basic TTL counters; others are listed in Appendix 3.

**TABLE 8-2. TTL COUNTERS**

| Number | nber Type                        |  |

|--------|----------------------------------|--|

| 7490   | Decade                           |  |

| 7492   | Divide-by-12                     |  |

| 7493   | Divide-by-16                     |  |

| 74160  | Presettable decade               |  |

| 74161  | Presettable divide-by-16         |  |

| 74190  | Up-down presettable decade       |  |

| 74191  | Up-down presettable divide-by-16 |  |

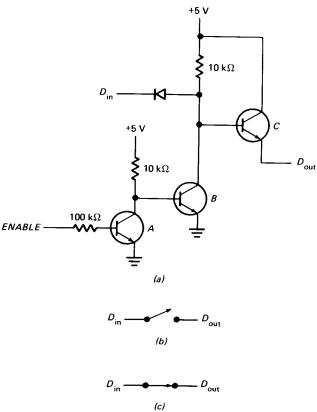

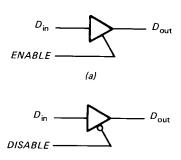

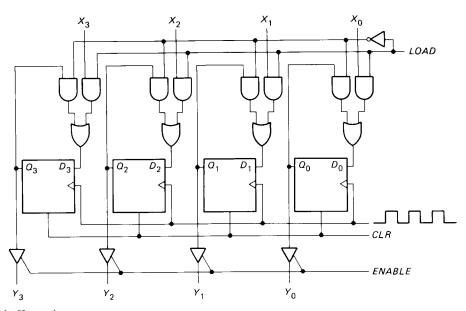

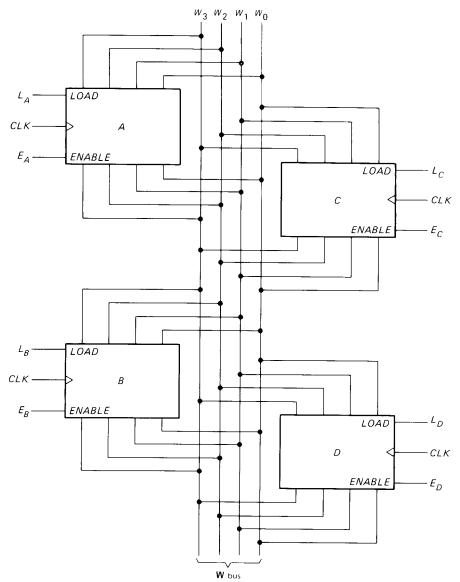

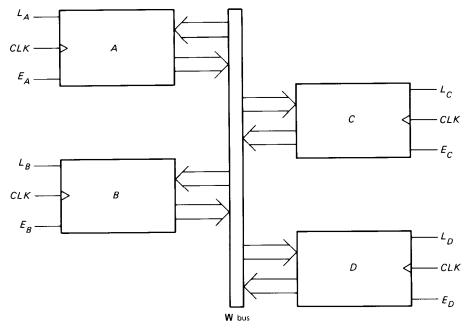

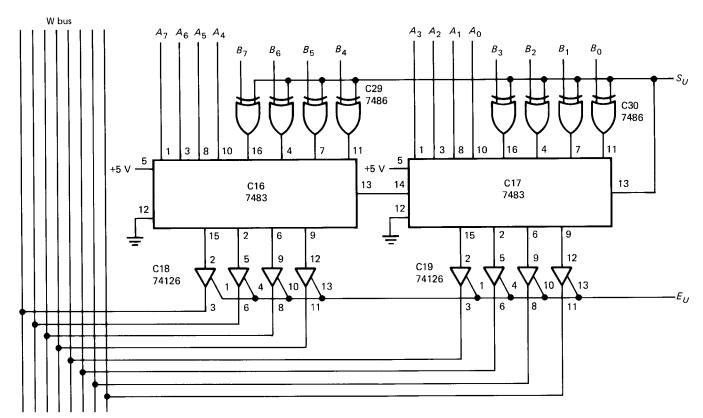

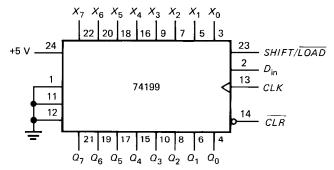

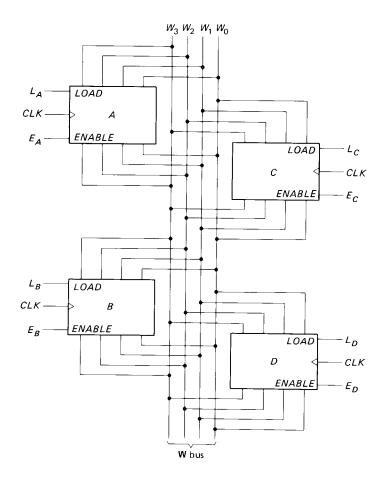

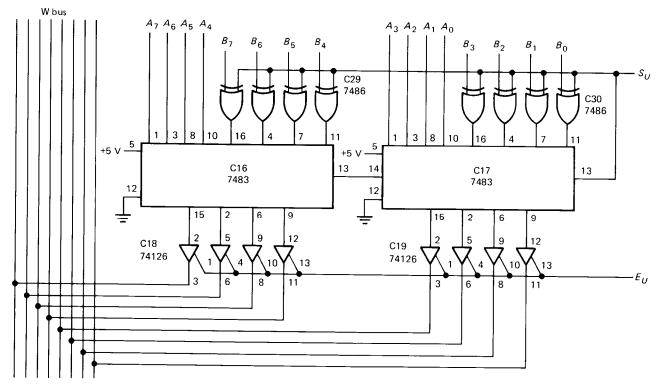

## 8-8 THREE-STATE REGISTERS